概要

TSMCは2026年4月22日のシンポジウムで、2029年までの半導体プロセスロードマップを発表した。CoWoS技術は2028年に14レチクル、2029年には40レチクル級のSoW-Xで量産予定。2nmプロセスの拡張版「N2U」は、速度向上や消費電力削減を実現し、2028年の生産開始を目指す。

詳細

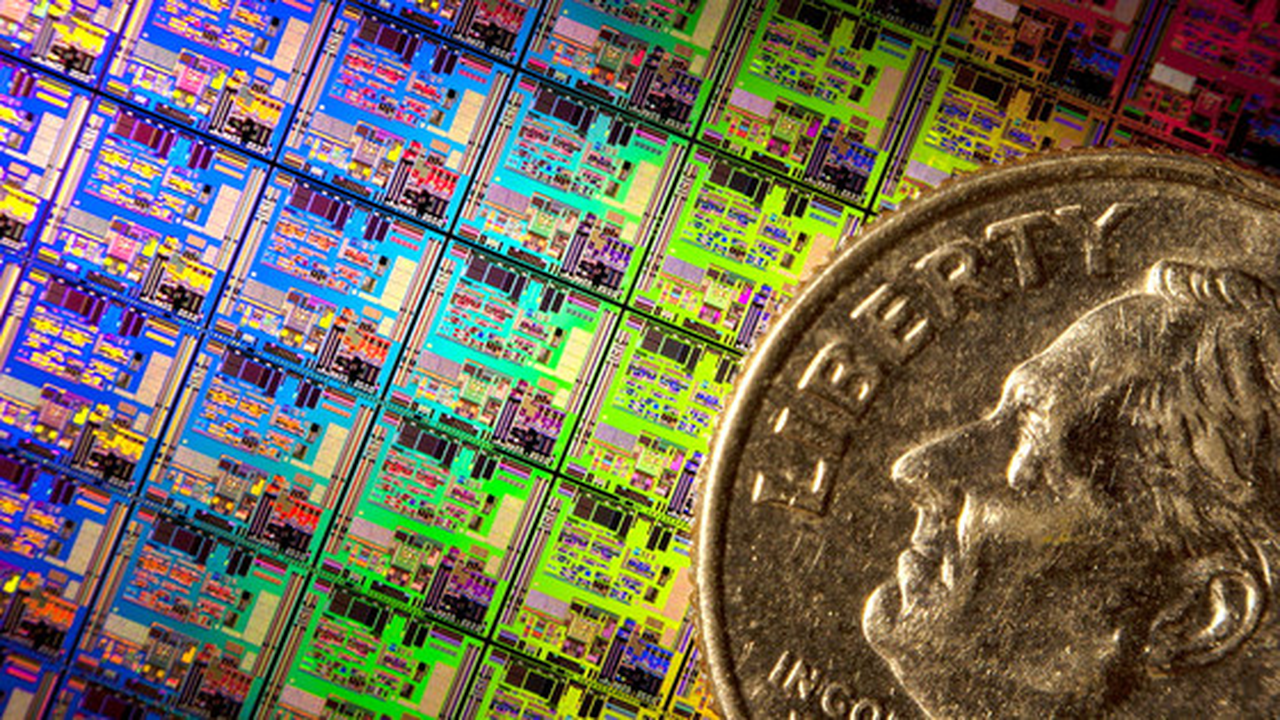

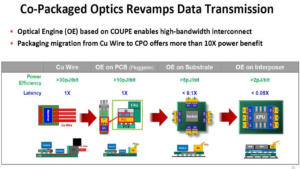

TSMCは2026年4月22日に開催されたNorth America Technology Symposium 2026で、2029年までを見据えた新たな半導体プロセスのロードマップを公開した。2.5D積層パッケージ技術であるCoWoSは、すでに生産中の5.5レチクル品に加え、2028年には大型計算ダイ約10個とHBM20スタック前後を統合できる14レチクル分の面積で量産する予定である。さらに2029年には、40レチクル級のSoW-X(巨大集積回路)の量産も見込まれている。また、2nmプロセス技術の拡張版である「N2U」は、N2Pに対して3〜4%の速度向上、または同一速度で8〜10%の消費電力削減、1.02〜1.03倍のロジック密度向上を実現し、2028年の生産開始を予定している。このロードマップは、AIや高性能コンピューティング(HPC)の需要増大に対応するため、微細化と高密度パッケージングの両面から技術革新を加速させるTSMCの戦略を示している。

関連情報

元記事: https://vertexaisearch.cloud.google.com/grounding-api-redirect/AUZIYQFL0-HksdUKN

コメント