パッケージング– category –

-

ASEテクノロジー:先進パッケージング新時代の到来と市場戦略

概要 ASEテクノロジーは、TSMCのCoWoS供給不足を背景に、先進パッケージング市場で強力な地位を確立しています。HBM統合やチップレット技術に不可欠な熱圧縮ボンディング(TCB)やハイブリッドボンディングの採用が拡大しています。同社の先端パッケージン... -

Adeia:ハイブリッドボンディング技術でHBMチップ革新を推進

概要 Adeia Inc.は、従来のペイTV特許事業から転換し、次世代HBMチップに不可欠なハイブリッドボンディング技術の主要プレーヤーを目指しています。ムーアの法則の限界が近づく中、チップレットとヘテロジニアス統合が重要になり、高性能ボンディング技術... -

エプソンとマンツ台湾、インクジェット技術で半導体アドバンストパッケージングを革新

概要 セイコーエプソンとManz Taiwanは、半導体製造プロセス、特にアドバンストパッケージング分野におけるインクジェット技術の普及を目指し、戦略的協業を開始しました。この提携は、エプソンの高精度プリントヘッド技術とManz Asiaの装置・ソフトウェア... -

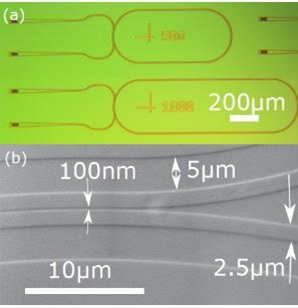

フォトニック集積プラットフォームおよびパネルレベルパッケージング向け薄膜堆積技術の進展

概要 ドイツのフラウンホーファーFEPが開発した新技術は、フォトニック集積プラットフォーム(PIC)およびパネルレベルパッケージング(PLP)に不可欠な能動・受動薄膜の堆積を可能にします。この技術により、導波路構造用のSi3N4などの受動材料、および高... -

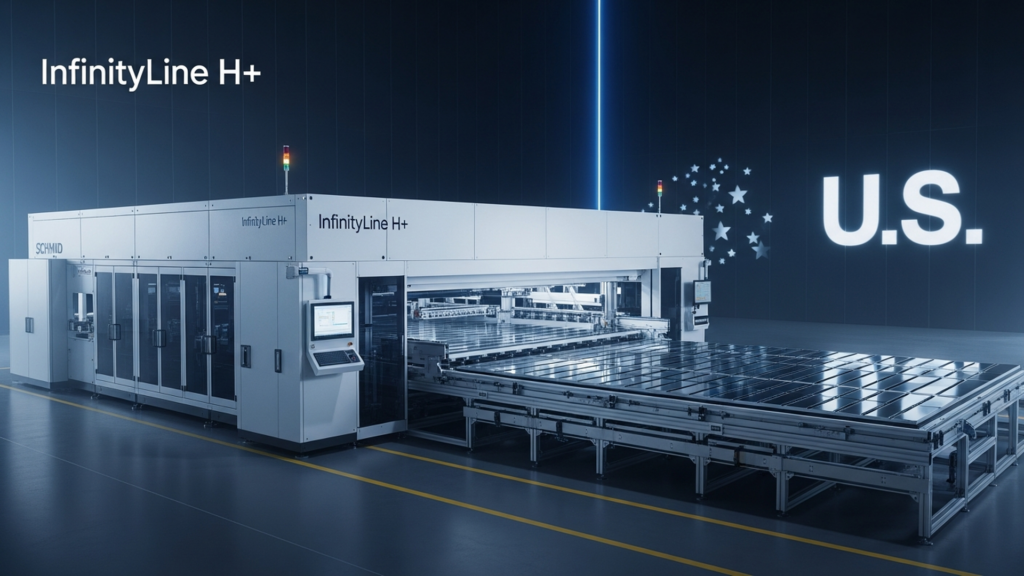

SCHMID、700x700mm対応パネルレベルパッケージング用InfinityLine H+を米国大手企業に納入

概要 ドイツのテクノロジー企業SCHMIDグループは、最大700×700mmの大判に対応するパネルレベルパッケージング(PLP)用の特殊システム「InfinityLine H+」の米国大手テクノロジー企業への初の納入を発表しました。このプラットフォームは、次世代基板製造... -

SamsungとAMDが次世代GPU「AMD Instinct MI455X」向けにHBM4で戦略的提携を締結

概要 AI半導体の性能を左右する後工程・メモリ分野において、SamsungとAMDが次世代高帯域幅メモリ「HBM4」に関する戦略的提携を結びました。この提携により、SamsungはAMDの次世代GPU「AMD Instinct MI455X」向けにHBM4を供給するMOUを締結。Samsungの最新... -

AIがPLPとガラスコアによる先進パッケージングへの移行を加速

概要 この業界分析は、AIがパネルレベルパッケージング(PLP)およびガラスコア基板の採用をどのように推進しているかを議論しています。Yole Intelligenceの予測を引用し、TSMCの「CoPoS」(Chip-on-Panel-on-Substrate)のロードマップと、ウェハに対す... -

AmkorのHDFO立ち上げが加速

概要 Amkor Technologyは、AIデータセンターの需要に対応するため、高密度ファンアウト(HDFO)パッケージングプラットフォームの立ち上げを加速しています。同社は韓国とベトナムで生産能力を拡大しており、HDFOを2026年の主要な収益ドライバーとして位置... -

Rapidus、2nm生産と先端パッケージング支援のため17億ドルを確保

概要 Rapidus Corporationは、日本政府および民間投資家から約17億ドルの新規資金を確保しました。この資金は、2027年までの2nmロジックチップの量産と、ガラス基板の検討を含む先進バックエンドパッケージングの開発を支援します。 詳細 Rapidusの資金調... -

ACM Research、複数の先進パッケージング装置を受注

概要 ACM Researchは、グローバル顧客からUltra C vac-pパネルレベル真空洗浄装置の新規受注を発表しました。この装置は、ファンアウトパネルレベルパッケージング(FOPLP)用に設計されており、真空技術を使用して微細ピッチ構造からフラックス残渣を除去... -

ASE、全自動310mmラインでパネルレベルパッケージング推進を加速

概要 ASE Technology Holdingは、2026年までに新しい全自動310mm生産ラインを稼働させ、ファンアウトパネルレベルパッケージング(FOPLP)の展開を加速しています。この動きは、CoWoSの容量制約を緩和し、急増するAIチップ需要に対応することを目的として... -

TSMC、次世代パッケージング技術「CoPoS」への移行を準備 750×620mmの巨大パネルを採用へ

【概要】 世界最大の半導体製造メーカーであるTSMCが、AIチップなどの高性能な半導体を組み立てる新しい方法「CoPoS(コポス)」の導入を進めています。これまでの丸い板(ウェハー)を使う方法から、巨大な四角いパネルを使う方法に切り替えることで、一...

1