背景:AIチップ需要の爆発とパッケージングの限界

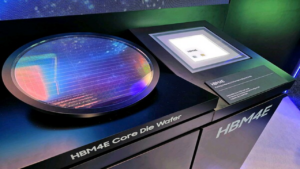

AIチップの需要が爆発的に増加する中、半導体の性能向上は微細化技術だけでなく、高度なパッケージング技術に大きく依存するようになっています。特に、複数のチップレットやHBM(高帯域幅メモリ)を統合する2.5Dおよび3Dパッケージングが不可欠です。TSMCのCoWoS(Chip on Wafer on Substrate)は、この分野で長らく業界を牽引してきましたが、さらなる高性能化とコスト効率の改善が求められています。

主要内容:CoPoSへの戦略的移行と独占供給体制の構築

TSMCは、AI半導体市場でのリーダーシップを揺るぎないものにするため、CoWoSの生産能力を拡大しつつ、より技術的に先進的なパネルレベルパッケージング(PLP)技術であるCoPoS(Chip on Panel on Substrate)の開発に注力していると報じられています。CoPoSは、円形のウェハーではなく四角いパネルを基板として使用することで、より大きな面積に多数のチップを配置でき、生産効率とコストパフォーマンスを向上させる可能性を秘めています。報道によると、TSMCはこのCoPoS技術のサプライチェーンにおいて、厳格な機密保持契約を台湾の設備・材料パートナーと締結しており、技術流出防止と量産後数年間のTSMCへの独占供給を確実にするよう求めているとのことです。これにより、TSMCは次世代パッケージング技術における競争優位性を確保し、AIチップ市場の支配を盤石にする狙いがあります。

- CoPoSの技術的優位性: CoPoSは、CoWoSと比較して、より高い統合密度と大型フォームファクタを実現できる可能性があり、AIアクセラレータや高性能コンピューティングの将来的な要件を満たす上で重要となります。

- 市場競争の激化: この独占供給戦略は、Intelなどの競合他社が独自のパッケージング技術(EMIBなど)を推進する中で、TSMCがそのリーダーシップを維持しようとする強い意志を示しています。

- サプライチェーンへの影響: TSMCの要求は、台湾のサプライチェーンパートナーに大きな影響を与え、彼らの技術開発と市場展開の方向性を規定する可能性があります。

影響と展望:AI半導体市場の未来像

TSMCのCoPoSへの積極的な投資と独占供給戦略は、AI半導体市場の未来を形成する上で重要な要素となります。この動きは、高性能コンピューティングとAIアプリケーションの進化に伴い、パッケージング技術が半導体産業の新たな成長ドライバーであることを強調しています。CoPoSが実用化されれば、現在CoWoSが直面している容量制約やコスト課題を緩和し、より多くのAIチップメーカーが先進パッケージングの恩恵を受けられるようになる可能性があります。しかし、その独占的な性質は、長期的な市場競争や技術革新のダイナミクスにどのような影響を与えるか、引き続き注視が必要です。将来的には、CPO(Co-Packaged Optics)のようなさらなる革新技術との連携も視野に入れ、AIデータ伝送のボトルネック解消にも貢献することが期待されます。

元記事: https://www.digitimes.com/news/a20260508PD207/tsmc-packaging-cowos-expansion-capacity.html

コメント