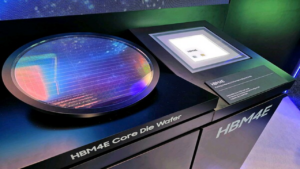

背景:3D積層技術がAI・HPC性能を限界突破

AI(人工知能)や高性能コンピューティング(HPC)の設計がますます複雑化し、性能要求が高まるにつれて、従来の2D平面でのチップスケーリングは物理的な限界に直面しています。この課題を克服するために、異なるチップレットを垂直方向に積層する3Dチップ積層技術が不可欠なソリューションとして浮上しています。特に、TSMCが推進するSoIC(System on Integrated Chips)は、この分野の最先端を走る技術の一つであり、パッケージングが半導体性能向上に直接貢献する時代を牽引しています。

主要内容:TSMC SoICの微細化ロードマップ

TSMCは、2026年北米技術シンポジウムにおいて、そのSoIC技術の最新ロードマップを発表しました。この更新されたロードマップは、SoICにおけるインターコネクトピッチを継続的に微細化する計画を示しており、これにより3D積層チップの統合密度を劇的に向上させることを目指しています。

- ピッチ微細化の目標: 現在のSoIC技術におけるインターコネクトピッチは6µmですが、TSMCは2029年までにこれを4.5µmへと縮小する目標を掲げています。このピッチ縮小は、ハイブリッドボンディングによって積層されたダイ間の垂直インターコネクト密度に直接影響し、データ転送効率と電力効率を大幅に向上させます。

- 高性能ノードとの連携: TSMCは、2029年にA14-on-A14 SoICの生産開始を予定しており、これはN2-on-N2 SoICと比較して1.8倍のダイ間I/O密度を実現すると発表しました。これは、最先端のプロセスノードで製造されたチップレットが、SoICによる3D積層を通じて、さらに高い性能を発揮できることを意味します。

- 3DFabricファミリーの一部: SoICは、CoWoS(Chip on Wafer on Substrate)やInFO(Integrated Fan-Out)といったTSMCの幅広い3DFabric先進パッケージングファミリーの中核をなす技術として位置付けられています。これにより、顧客は多様なアプリケーション要件に応じた最適なパッケージングソリューションを選択できるようになります。

影響と展望:次世代AI・HPC設計への道筋

TSMCのSoICロードマップの進展は、次世代のAIおよびHPCアプリケーション設計にとって極めて重要な意味を持ちます。インターコネクトピッチの微細化は、より多くの機能ブロックを限られたフットプリントに統合することを可能にし、AIアクセラレータの処理能力、消費電力、およびメモリ帯域幅を飛躍的に向上させます。この技術は、従来のムーアの法則の限界を超える新たな性能スケーリングの道を開くものであり、半導体業界全体のイノベーションを加速させるでしょう。将来的には、SoICのような3D積層技術が、オンチップシステム全体の性能を決定する主要な要素となり、複雑な異種統合システムの実現に向けた基盤を築くことが期待されます。

元記事: https://www.design-reuse.com/news/202530447-tsmc-soic-roadmap-targets-2029-chip-stacking/

コメント