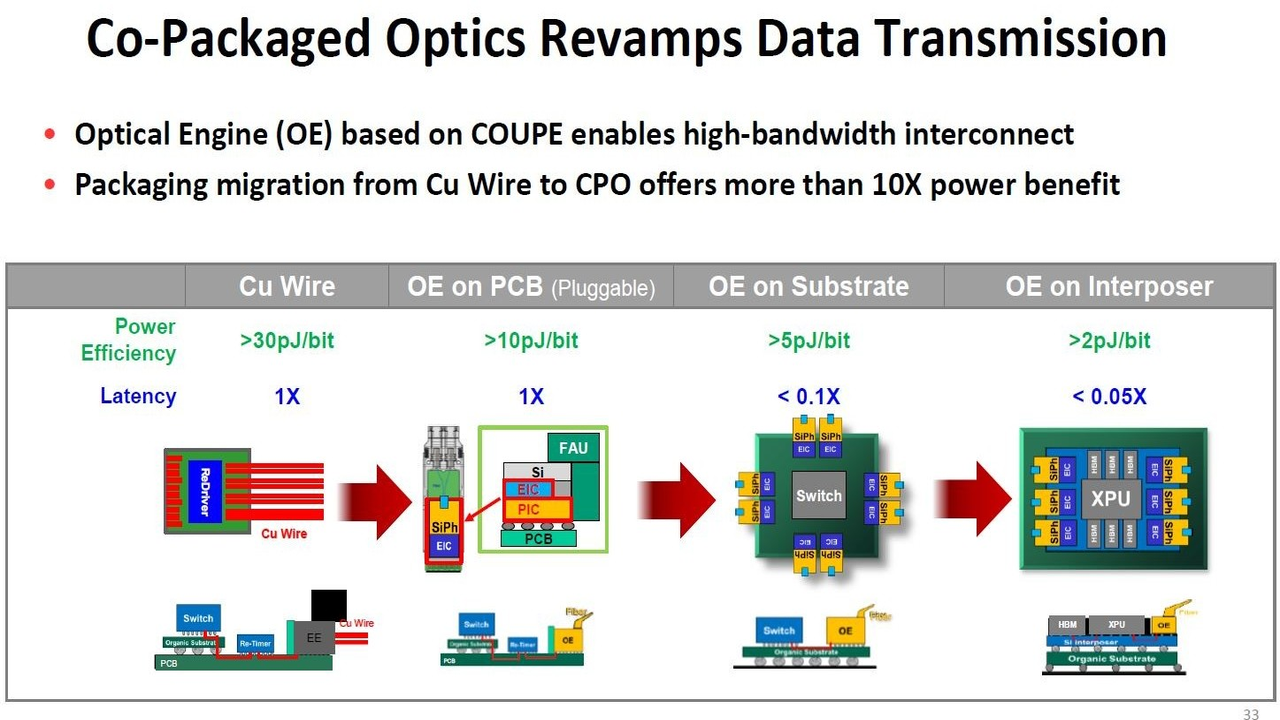

EE Times Japanの記事は、TSMCがIEDM 2025で解説した「シリコンフォトニクスと先進パッケージの統合」に焦点を当てる。James Chen氏の講演に基づき、AI/HPC向け先端パッケージングとチップレット技術を詳述。次世代技術として「COUPE技術」による光電融合が紹介され、データ伝送の高速化と低消費電力化の可能性が示された。これは、2.5D/3D実装における電気配線のボトルネックを解消し、AIチップ性能向上に不可欠。日本の半導体産業、特にRapidusの光電融合重視の観点からも重要だ。

EE Times Japanが2026年4月24日に公開した記事では、TSMCが国際学会IEDM 2025で解説した最新のパッケージング技術シリーズの第13回として、「シリコンフォトニクスと先進パッケージの統合が描く未来」に焦点を当てている。TSMCのAdvanced Package Integration Division R&DディレクターであるJames Chen氏の講演内容に基づき、AIおよびHPC(高性能コンピューティング)向け先端パッケージング技術と先端チップレット技術について詳述。特に、次世代の先進パッケージ技術として「シリコンフォトニクス」(COUPE技術)が紹介され、光電融合によるデータ伝送の高速化と低消費電力化の可能性が示されている。この技術は、複数の回路ダイを積層する2.5D/3D実装において、従来の電気配線のボトルネックを解消し、AIチップの性能向上に不可欠となる。日本の半導体産業にとっても、ラピダスが光電融合技術を重視していることからも、この分野の動向は極めて重要である。これは、グローバルな先端半導体技術の最前線を示し、日本の半導体戦略、特に後工程技術開発の方向性に大きな影響を与える情報だ。

元記事: https://vertexaisearch.cloud.google.com/grounding-api-redirect/AUZIYQGsfMcP6k473

コメント