概要

TSMCは2026年4月22日のシンポジウムで、次世代プロセス「A13」を発表した。A14プロセスを基盤とし、チップ面積を約6%削減し、2029年の量産開始を目指す。AIやHPC向け需要に対応するため、電力効率改善と高密度実装を推進。CoWoS技術の拡張により、NVIDIAやAMDのAIアクセラレーター向け高密度実装を強化する。

詳細

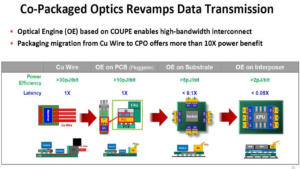

TSMCは2026年4月22日、米カリフォルニア州サンタクララで開催された「2026年TSMC北米テクノロジー・シンポジウム」で、AI時代の半導体ロードマップの一環として、A14プロセスを基盤とする次世代プロセス「A13」を発表した。A13はA14と比較してチップ面積を約6%削減し、電力効率を改善することで、2029年の量産開始を目指す。この技術は、AIや高性能コンピューティング(HPC)向け需要の急増に対応する中核技術の一つと位置づけられている。また、TSMCが開発した先進パッケージング技術であるCoWoS(Chip on Wafer on Substrate)は、複数のチップ(ロジックダイ、HBMなど)をシリコンインターポーザー上に並べて高密度に統合するもので、NVIDIAやAMDのAIアクセラレーターで広く採用されている。CoWoSの拡張によりAI向け高密度実装を推進し、ダイ間の帯域を高める新たな3Dチップ積層技術も打ち出しており、AI半導体の性能向上と供給能力確保に貢献する。

関連情報

元記事: https://vertexaisearch.cloud.google.com/grounding-api-redirect/AUZIYQEMQYXLndoqr

コメント