先進パッケージング市場の進化とファンアウト技術の重要性

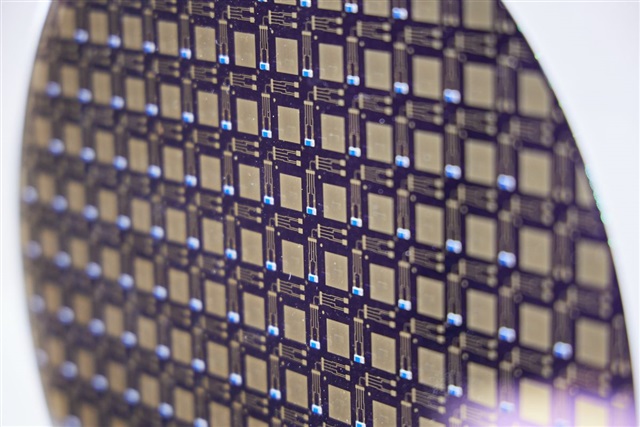

半導体業界は、ムーアの法則の物理的限界に近づく中で、チップの性能向上を継続するための新たなアプローチを模索しています。その主要な方向の一つが、半導体後工程における先進パッケージング技術の革新です。特にファンアウト(Fan-Out)パッケージングは、従来のパッケージング手法よりも高密度で、チップを効率的に統合できるため、AI、HPC、モバイルデバイスといった高性能が要求されるアプリケーションにおいてその重要性を増しています。ファンアウト技術は、シリコンウェーハから切り出したチップを再構成ウェーハやパネル上に配置し、その上で再配線層(RDL)を形成することで、入出力(I/O)端子数を増やし、パッケージサイズの縮小と電気的特性の向上を両立させます。

FOPLPとWMCMが牽引する技術革新

現在、ファンアウトパッケージング市場において、特に注目されているのが以下の二つの技術です。

- ファンアウト・パネルレベル・パッケージング(FOPLP: Fan-Out Panel-Level Packaging): これは、従来の円形ウェーハではなく、ディスプレイ製造に用いられる大型の長方形パネル基板を利用してチップをパッケージングする手法です。パネルサイズが大きいため、一度に処理できるチップ数が増え、生産効率とコスト効率が大幅に向上します。AIアクセラレーターやHPC用チップなど、大規模なシステムにおいて特にメリットが大きいです。

- マルチチップモジュール(WMCM: Wafer-Level Chip-Scale Package Multi-Chip Module): これは、ウェーハレベルチップスケールパッケージ(WLCSP)の技術を応用し、複数のチップを単一のパッケージ内に統合するアプローチです。チップレット技術と組み合わせることで、異なる機能を持つチップを組み合わせ、システム全体の性能と柔軟性を高めることが可能です。

これらの技術は、特にAIモバイルデバイスや高性能計算(HPC)といった分野で求められる、コストと性能のバランスの取れたソリューションとして急速に普及が進んでいます。記事によると、ASE(日月光投控)やPowertech(力成科技)といった主要なOSAT(Outsourced Semiconductor Assembly and Test)プロバイダーは、AIブームの恩恵を受けるべく、FOPLPへの投資を強化しています。例えばASEは、2026年までに完全自動化された310mmラインでのパネルレベルパッケージングを加速しており、これはより大きなフォーマットでのパッケージングへの戦略的な移行を示唆しています。

業界競争と今後の展望

ファンアウトパッケージングは、ファウンドリとOSATプロバイダーの両方にとって、新たな競争領域となっています。TSMC、Intel、Samsungといったファウンドリ大手も独自の先進パッケージング技術を開発・提供しており、OSAT企業は差別化とコスト効率の向上を追求することで競争力を維持しようとしています。FOPLPのような大型パネルフォーマットの導入は、生産スループットを劇的に向上させ、スケールメリットによるコスト削減を可能にするため、今後の競争環境において重要な要素となるでしょう。先進パッケージング技術の進化は、AIチップの性能をさらに引き出し、次世代の電子機器やデータセンターのインフラを支える基盤となります。この分野への継続的な投資と技術革新は、半導体産業全体の成長を促進し、より高性能で効率的なコンピューティングソリューションの実現に不可欠です。

元記事: https://www.digitimes.com/news/a20260407PD203/packaging-foplp-market-production-capacity.html

コメント