AI時代の高性能チップ需要と先進パッケージングの競争激化

人工知能(AI)の急速な発展は、データセンターやクラウドコンピューティングにおける高性能チップの需要を前例のないレベルに押し上げています。特に、AIアクセラレーターやASIC(特定用途向け集積回路)の開発においては、複数のチップを効率的に統合する先進パッケージング技術が、チップの性能、消費電力、そしてコストを決定づける重要な要素となっています。現在、この分野ではTSMCがCoWoS(Chip on Wafer on Substrate)で先行していますが、その能力のひっ迫が深刻化しており、顧客は代替ソリューションを模索する状況にあります。このような背景から、Intelが自社の先進パッケージング技術で市場での存在感を高めています。

IntelのEMIBとFoveros技術の台頭

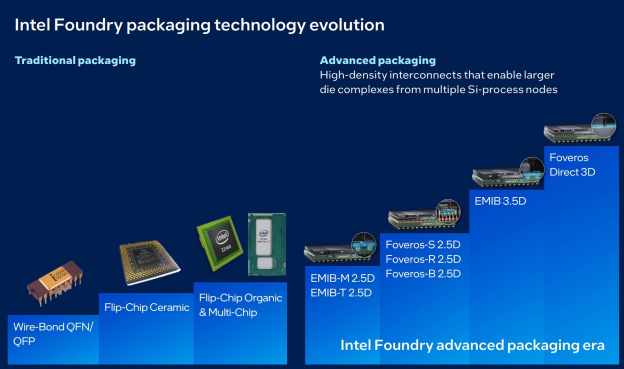

Intelの先進パッケージング事業は、GoogleやAmazonといった主要なクラウドプロバイダーおよびAI開発企業との協業を通じて、勢いを増していると報じられています。これらの企業は、自社開発のAIチップ(GoogleのTPUやAmazonのTrainiumなど)のASIC開発およびパッケージングサービスにおいて、Intelの技術の採用を検討しているとのことです。特に注目されているのは、IntelのEMIB-T(Embedded Multi-die Interconnect Bridge)統合技術です。EMIBは、異なるプロセスノードで製造された複数のチップレットを、高速かつ電力効率よく統合することを可能にする技術であり、TSMCのCoWoS能力に代わる魅力的な選択肢として浮上しています。

Intelはまた、Foverosと呼ばれる3Dスタックパッケージング技術も展開しており、これらはチップレット設計とヘテロジニアス統合のトレンドを加速させる上で重要な役割を担っています。顧客がTSMCのCoWoS能力確保に苦慮する中で、IntelはEMIBやFoverosを、特に米国国内における信頼できるセカンドソースとして積極的に売り込んでいます。Intelは、先進パッケージングを今後の主要な成長ドライバーと位置付け、マレーシアやニューメキシコでも関連施設の拡張を進めています。ニューメキシコのFab 9とFab 11Xでは、すでに3D先進パッケージング技術の量産が行われています。この動きは、AIおよびHPCチップのパッケージング需要を巡る競争が激化していることを明確に示しています。

TSMCの対抗策と業界への影響

Intelの動きに対し、TSMCも米国での能力拡張を加速させています。アリゾナ州に先進パッケージング施設を建設する計画があり、2026年第2四半期に着工し、2027年後半から2028年の間に稼働開始を目指しています。ここでは、SoIC(System on Integrated Chips)、CoW(Chip on Wafer)、CoPoS(Chip on Package on Substrate)といった技術を用いて、米国内のAIおよびHPCチップのパッケージング需要をサポートする予定です。この動きは、米国内での半導体サプライチェーンのレジリエンス強化という地政学的な側面も持ち合わせています。先進パッケージング市場におけるIntelとTSMCの競争は、技術革新をさらに加速させ、顧客にとっては選択肢の拡大とサプライチェーンリスクの低減というメリットをもたらすでしょう。最終的には、AIチップの性能向上とコスト効率化に貢献し、AI技術のさらなる普及を後押しすることが期待されます。

コメント