背景:AI時代のメモリウォールとHBMの重要性

人工知能(AI)技術の急速な発展、特に大規模言語モデル(LLM)や複雑なディープラーニングアルゴリズムの進化は、半導体チップの演算能力に対する要求を飛躍的に高めています。しかし、CPUやGPUの演算能力が向上しても、データと演算ユニット間のボトルネック、いわゆる「メモリウォール」が、AI処理性能向上の主要な制約となっています。この課題を克服するために、高帯域幅メモリ(HBM: High Bandwidth Memory)は不可欠なソリューションとして登場しました。

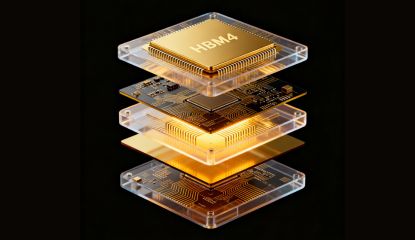

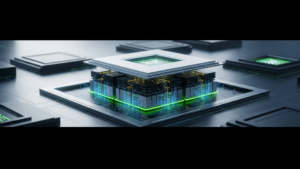

HBMは、DRAMダイを垂直に積層し、プロセッサに近接して配置することで、従来のDDRメモリに比べて圧倒的に広いデータ帯域幅と高い電力効率を提供します。2026年のAI革命を牽引するHBM4のような次世代HBMは、さらに高い性能と集積度を要求され、その製造には先進パッケージング技術と材料革新が不可欠となっています。この進化は、メモリが単なるコモディティではなく、AIシステムの性能を左右する「戦略的資産」へとその位置づけを変えていることを示しています。

主要内容:HBM4と3D DRAMによるメモリウォール打破

本記事は、2026年のAI革命におけるHBM4と3D DRAMの極めて重要な役割に焦点を当てています。SK Hynix、Samsung、Micronといった大手メモリメーカーは、NVIDIAのVera Rubinアーキテクチャのような大規模AIチップ向けにHBM4の量産体制を確立しています。HBM4は、メモリの「ハイウェイ」、すなわちメモリバス幅が2048ビットに倍増しており、これによりデータ転送能力が大幅に向上しています。

- データ転送能力の強化: HBM4の2048ビットのメモリバス幅は、HBM3Eの1024ビットから倍増しており、AIプロセッサが必要とする膨大なデータを高速で供給することを可能にします。これは、AIモデルの学習と推論のボトルネックを緩和し、全体的な処理性能を向上させます。

- ハイブリッドボンディング技術の採用: Samsungは、HBM4スタックにハイブリッドボンディング技術を導入しています。この技術は、ダイ間の直接的な銅-銅接合を可能にし、従来の半田バンプよりも高密度で優れた熱特性を実現します。これにより、チップの発熱が抑制され、HBM4がより長い時間、最大速度で動作できるようになり、デバイスの信頼性と寿命が向上します。

- 戦略的投資の拡大: メモリの重要性が高まる中、Micronは2026年の予算をHBM4の需要に対応するためだけに200億ドルに増額すると報告されています。これは、HBMがAIサプライチェーンにおいて、いかに不可欠なコンポーネントとなっているかを示すものです。

影響と展望:半導体産業におけるメモリの新たな位置づけ

HBM4と3D DRAMの進化は、半導体産業におけるメモリの新たな位置づけを確立しています。メモリは、単なるストレージコンポーネントではなく、AIシステムの性能と効率を決定する戦略的な要素へと変貌しました。この変化は、メモリメーカーとAIチップ設計者の間の協力関係を深化させ、HBM技術のさらなるイノベーションを促すでしょう。

また、ハイブリッドボンディングのような先進パッケージング技術の採用は、HBMの性能向上だけでなく、将来の3D積層チップレットアーキテクチャの実現に向けた基盤を築きます。これにより、チップ設計者は、ムーアの法則の限界を超えて、より複雑で高性能なシステムを構築するための新たな道筋を見出すことができます。HBM4の量産体制の確立とそれに伴う巨額の投資は、AIチップ市場の爆発的な成長を支えるとともに、半導体サプライチェーン全体におけるメモリの戦略的価値を一層高めることになるでしょう。

コメント