背景と3Dパッケージング技術の課題

現代の電子システムでは、さらなる小型化、高性能化、低消費電力化が求められており、これを実現する技術として3D TSV(Through-Silicon Via)先進パッケージングが注目されています。複数のチップを垂直に積層し、TSVを介して電気的に接続することで、従来の2Dパッケージングに比べて劇的な集積度の向上と配線遅延の短縮が可能となります。しかし、この技術の導入には、製造プロセスの複雑性、特にウェハーの反り(Warpage)の制御が大きな課題として立ちはだかります。反りは、マイクロバンプの接続不良、アンダーフィル材料の不均一な充填、さらにはチップのクラックといった致命的な欠陥を引き起こし、製品の電気的歩留まりと長期信頼性を著しく低下させる可能性があります。

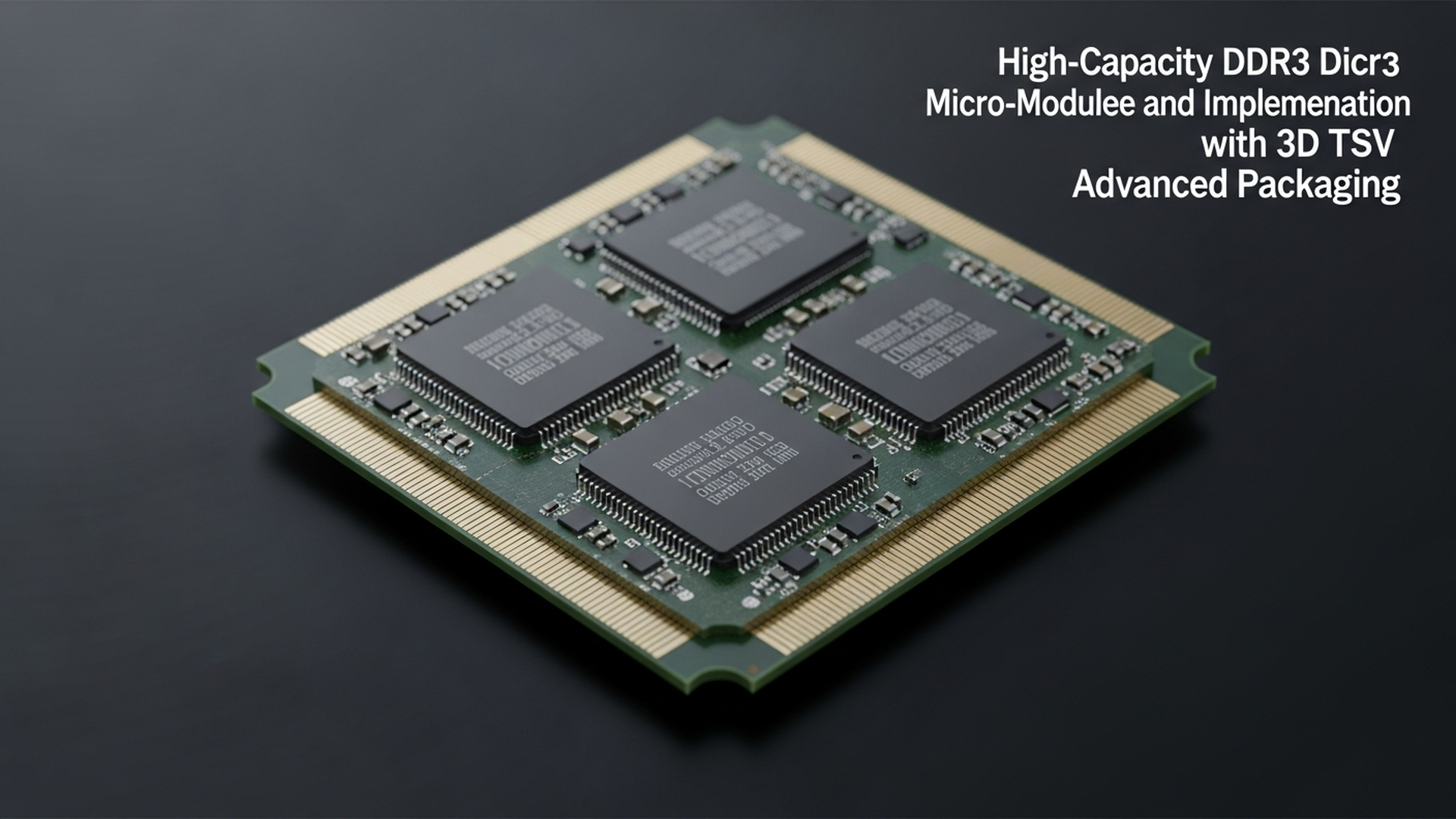

DDR3マイクロモジュールの設計と実装

本研究では、この課題に対し、ウェハーレベルパッケージングと3D TSV技術を組み合わせた4層積層DDR3マイクロモジュールのシステムレベル統合モデリングアプローチと具体的な設計手法を提案しています。異種チップファンアウト技術とTSVベースの垂直積層を駆使することで、物理的に非常にコンパクトな14 × 9 × 3.5 mmのフットプリントを実現しつつ、4 GBという高容量と64ビットのバス幅を達成しました。これにより、高性能コンピューティングや組み込みシステムなど、限られた空間で高いメモリ性能が要求されるアプリケーションへの適用が期待されます。

ウェハー反り制御の重要性 と将来展望

この高密度3Dパッケージングにおいて、ウェハーの反り制御は成功の鍵を握ります。研究では、反りシミュレーション、プロセスパラメータの実験計画法(DOE)による最適化、およびモデルキャリブレーションを系統的に実施することが、高い歩留まりで3D TSVパッケージングを実現するための必須条件であると指摘されています。これにより、製造過程における欠陥発生を未然に防ぎ、製品の信頼性を大幅に向上させることが可能となります。本研究は、高精度な反り予測と制御のための信頼できる方法論的基盤を提供し、現代の電子システムのさらなる小型化と高性能化を推進するための重要な一歩となるでしょう。将来的には、より高層化された積層構造や、さらに微細なTSVを用いた次世代メモリデバイスの開発に貢献することが期待されます。

コメント