OFC 2026における技術デモンストレーション

Marvell Technologyは、OFC 2026(光ファイバー通信会議)において、AIインフラストラクチャで使用されるXPU(eXtended Processing Units)向けの次世代ダイツーダイ相互接続技術における画期的な進歩を詳述しました。同社は、業界初の双方向64GbpsダイツーダイインターフェースIPを実演し、この技術が帯域幅、性能、効率、そして帯域幅密度において大幅な向上をもたらすことを示しました。

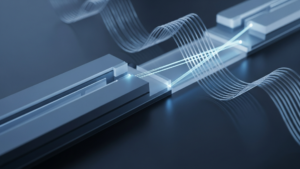

この技術革新は、特にAIアクセラレータやプロセッサ間のチップ内通信、さらにはコパッケージドオプティクス(CPO)などの先進的なパッケージングにおいて極めて重要です。ダイツーダイ相互接続は、複数のチップレットを単一のパッケージ内に統合するヘテロジニアスインテグレーションにおいて、チップレット間の高速かつ効率的なデータ転送を実現する基盤となります。64Gbpsという高いデータレートは、AIワークロードが要求する膨大なデータ量を処理するための必要条件であり、Marvellはこの分野で業界をリードするソリューションを提供しています。

信頼性の向上と電力効率

Marvellの新しいダイツーダイ相互接続技術は、単に速度を向上させるだけでなく、システムの信頼性にも重点を置いています。冗長レーンや自動レーン修復といった独自の信頼性機能が組み込まれており、これにより複雑なシステムにおける製造歩留まりの向上とビットエラー率(BER)の低減に貢献します。AIデータセンターのようなミッションクリティカルな環境では、システムの安定稼働が極めて重要であるため、これらの信頼性機能は非常に価値が高いです。

記事はまた、これらの進歩が、設計者が性能を大幅に向上させ、レイテンシを削減すると同時に、インターフェースに必要な消費電力とシリコン面積を削減することを可能にすると強調しています。電力消費の削減は、AIデータセンターの運用コストと環境負荷を低減する上で不可欠な要素であり、シリコン面積の削減は、より高密度な集積化と小型化を促進します。Marvellが達成した卓越した信号整合性と信頼性は、AIインフラのスケーリングに多大な影響を与えることが約束されています。

AIインフラへの深い影響

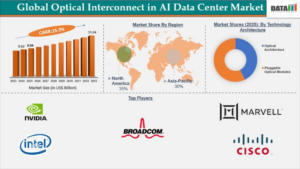

このような次世代のダイツーダイ相互接続技術は、AIインフラの設計と展開に深い影響を与えます。AIアクセラレータ、GPU、CPUといったXPUが、より高速に、より効率的に相互接続されることで、AIモデルのトレーニングと推論の速度が飛躍的に向上します。特に、コパッケージドオプティクス(CPO)との組み合わせにより、チップ間、ボード間、そしてラック間の通信ボトルネックが解消され、ギガワット級のAIクラスタの実現を加速するでしょう。

Marvellのこの技術は、AIの未来を支えるコンピューティングプラットフォームの基盤を強化し、高性能コンピューティングとデータ通信の境界をさらに曖昧にするものとして、業界内外から大きな注目を集めています。

元記事: https://www.marvell.com/blogs/next-generation-die-to-die-interconnects-for-xpus.html

コメント