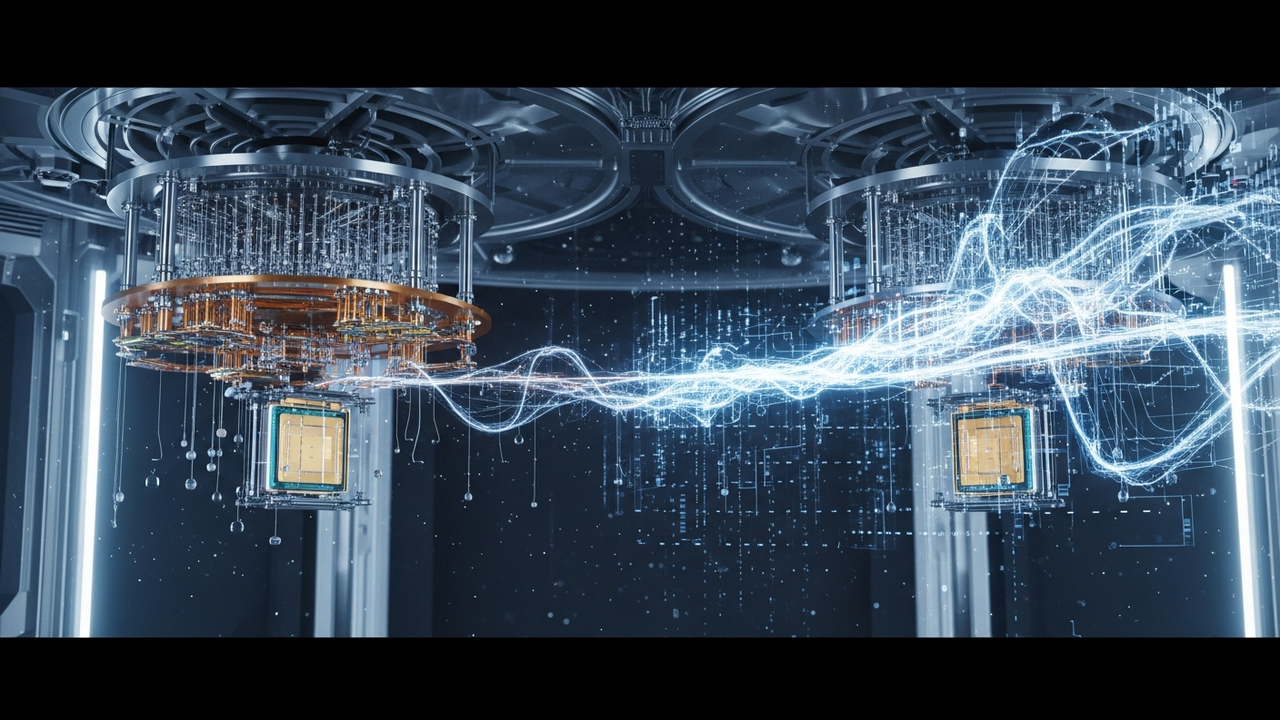

背景と量子誤り訂正の重要性

量子コンピュータがその真の可能性を発揮するためには、量子ビットが持つ脆弱性、すなわちノイズやデコヒーレンス(量子状態の崩壊)による計算エラーを克服する必要があります。この課題に対処するための最も重要な技術が量子誤り訂正(Quantum Error Correction, QEC)です。QECは、複数の物理量子ビットを用いて論理量子ビットを符号化し、エラーを検出・修正することで、計算の信頼性を高めることを目指します。しかし、QECの実装は極めて困難であり、現在の量子コンピュータの限られた物理量子ビット数と短いコヒーレンス時間では、高信頼性の耐障害性量子コンピュータを実現することは依然として大きな課題です。

物理とコードの統合アプローチ

arXiv.orgで発表された最新の研究は、QECアーキテクチャ設計における画期的な進展を提示しています。この研究では、これまで別々に扱われがちだった「物理量子ビットの制約と特性」(例: 接続性、エラーの種類、ノイズ源)と、「QECコードの理論的要件」(例: 必要な冗長性、測定戦略)とを統合する新しいフレームワークを提案しています。具体的には、タスク固有のハードウェア設計をQECコードと密接に連携させることで、より効率的かつ堅牢な量子コンピューティングアーキテクチャを実現しようとしています。

このアプローチの主要な特徴は以下の通りです。

- ヘテロジニアス・アーキテクチャ: 異なる種類の量子ビット(例: 超伝導量子ビットとイオントラップ)や、古典的な制御システムを統合し、それぞれの利点を最大限に活用。

- ハードウェア適応型QEC: 特定の物理ハードウェアのエラー特性に合わせてQECコードを最適化し、必要な物理量子ビット数を削減しつつ、エラー訂正能力を向上。

- リアルタイム・エラー検出と修正: 高速かつ低遅延でエラーを検出し、修正するための古典制御システムの最適化。

これにより、理論的なQECの効率性と、現実の物理デバイスが持つ制約との間のギャップを埋め、より実用的な耐障害性量子コンピュータの設計に向けた道を切り開きます。

影響と今後の展望

この統合されたQECアーキテクチャの研究は、量子コンピューティングの発展に多大な影響を与えることが期待されます。

- 耐障害性量子コンピュータの実現: エラー訂正の効率化は、大規模で実用的な量子コンピュータを構築するための最も重要なステップの一つです。この研究は、その実現時期を早める可能性を秘めています。

- スケーラビリティの向上: ハードウェアの制約を考慮に入れたQEC設計は、量子コンピュータのスケーラビリティを向上させ、より多くの量子ビットを効率的に利用できるようにします。

- 新たなハードウェア設計の指針: QECコードとハードウェア設計の統合は、将来の量子プロセッサ開発における新しい設計原則やアプローチを導き出すでしょう。

- アルゴリズム開発への影響: より信頼性の高い論理量子ビットが利用可能になることで、より複雑で深層な量子アルゴリズムの実装が可能になり、様々な科学技術分野での応用が加速されます。

この研究は、量子誤り訂正における基礎的な課題への革新的なアプローチを提供し、未来の量子コンピューティング技術の方向性を形作る重要な一歩と言えます。

元記事: #

コメント