AI時代におけるTSMCの比類なき地位

半導体産業において、TSMC(台湾積体電路製造)は単なるファウンドリ企業以上の存在となっています。2026年の時点で、同社は「世界のデジタル経済の中枢神経」と評されるほど、その技術力と生産能力が広範な産業の基盤を支えています。特に、人工知能(AI)が社会のあらゆる側面に浸透する「AIの時代」においては、TSMCの役割はこれまで以上に戦略的な重要性を持っています。高性能AIチップ、特にAIアクセラレーターは、膨大な計算能力とデータ帯域幅を要求し、これは最先端のプロセス技術と革新的なパッケージング技術なくしては実現できません。TSMCは、これらの要求に応えるための最前線に立っています。

先進パッケージング技術によるAIアクセラレーターの実現

TSMCの競争優位性を支える中核の一つが、その先進パッケージング技術です。記事では、CoWoS(Chip on Wafer on Substrate)とSoIC(System on Integrated Chips)が特に強調されています。これらの技術は、NVIDIAのRubinアーアーキテクチャのような次世代ハイエンドAIアクセラレーターの実現に不可欠です。

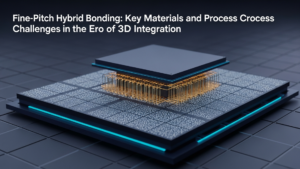

- CoWoS: 高帯域幅メモリ(HBM)とロジックチップ(GPUなど)を効果的に統合し、シリコンインターポーザー上に配置することで、チップ間の高速データ転送と高密度集積を実現します。これにより、AIワークロードに不可欠な膨大なメモリ帯域幅と計算能力を同時に提供できます。

- SoIC: チップレットを垂直方向に直接積層する技術で、従来のパッケージングよりもはるかに緊密な統合と性能向上を可能にします。これは、異種統合(Heterogeneous Integration)の究極形とされ、ムーアの法則の限界を超えてシステムレベルでの性能向上を追求する上で極めて重要な技術です。

これらの先進パッケージング技術は、AIチップが直面する性能、消費電力、およびフォームファクタの課題を解決する上で決定的な役割を果たしています。TSMCは、これらの技術を提供することで、NVIDIA、AMD、Google、Amazonといった主要なAI企業にとって「かけがえのないエンド・ツー・エンドの製造パートナー」としての地位を確立しています。

記録的な設備投資と将来への戦略

TSMCは、2025年度において顕著な収益と純利益の増加を達成し、強固な財務実績を示しました。さらに、同社は2026年に520億ドルから560億ドルという記録的な規模の設備投資を計画しています。この巨額の投資は、主に2nmおよび1.6nmといった次世代プロセスノードの生産能力増強、そしてCoWoSなどの先進パッケージング能力の拡張に向けられています。この戦略的な投資は、SamsungやIntelといった強力な競合他社に対してTSMCの技術的および市場的優位性を維持するための鍵となります。

TSMCの先進技術への継続的なコミットメントは、AI技術のさらなる発展を可能にし、世界の半導体産業における台湾のリーダーシップを盤石にするものです。AIチップ需要の増加に伴い、TSMCの先進パッケージング能力は、今後も世界のデジタル経済の成長を牽引する中核的な要素であり続けるでしょう。

コメント