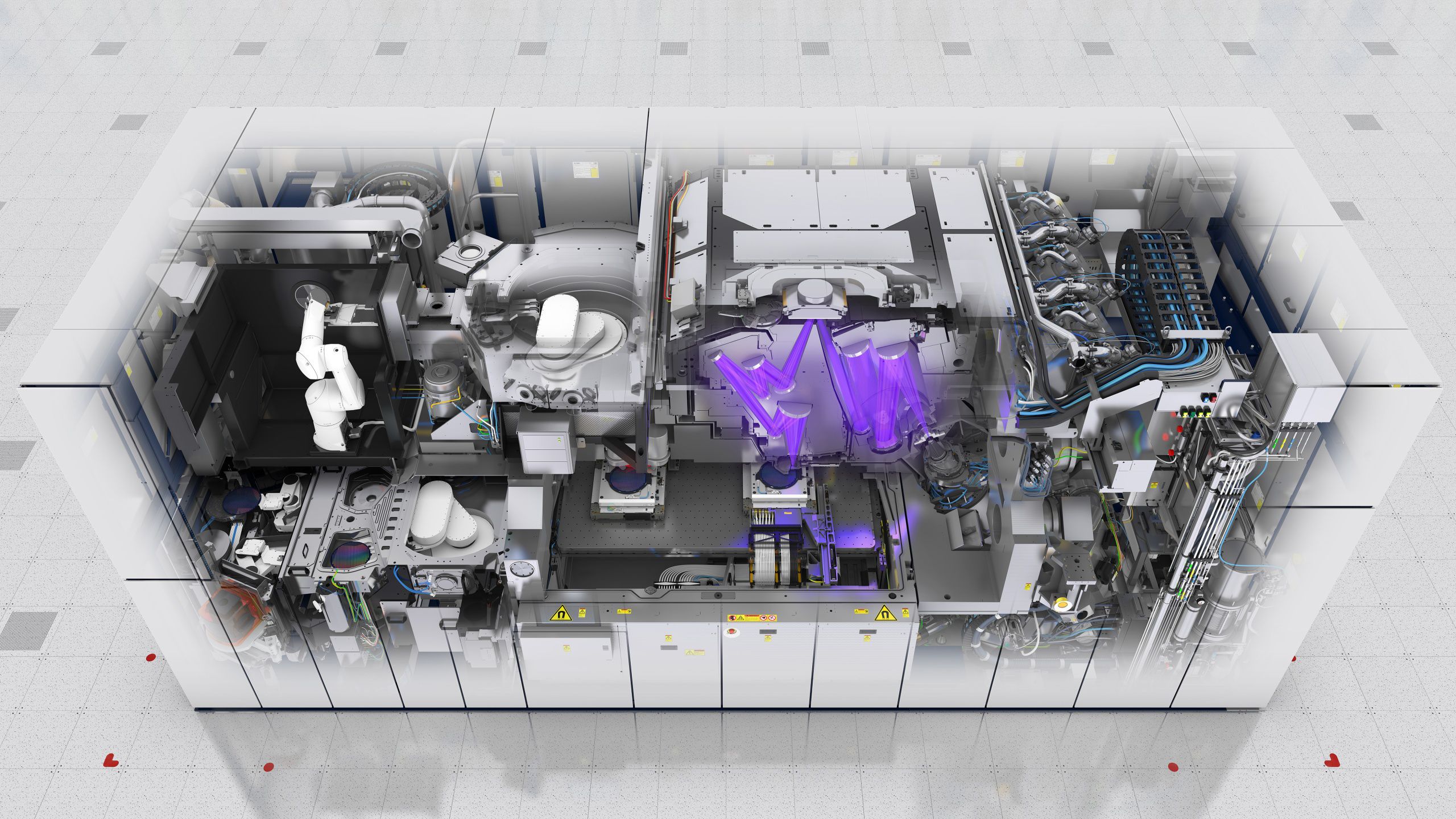

EUVリソグラフィにおける画期的な進歩

ASMLは、極端紫外線(EUV)リソグラフィにおける技術的ブレークスルー、すなわち、スキャナーのスループットを大幅に向上させる1000W電源を発表しました。現在の最先端システムは通常250Wから500Wで動作しています。新しい光源は、330ウェハ/時という生産性目標を可能にし、最先端ノード(2nm以降)のウェハあたりのコストを削減します。これは、より多くのチップをより迅速に生産できることを意味し、半導体製造の効率を劇的に向上させます。この技術革新は、ムーアの法則の限界に挑戦し続ける半導体業界にとって、極めて重要な一歩となります。

チップレット経済への直接的な貢献

これはウェハ製造技術ですが、チップレット経済に直接関連しています。チップレットの経済的実現可能性は、最先端のロジックダイを費用対効果の高い方法で製造できるかどうかにかかっています。これらの将来の機械で生産される2nmおよび1.4nmダイは、古いノードのI/Oダイやメモリスタックとともにパッケージ化される「頭脳」となります。つまり、フロントエンドでの微細化と生産効率の向上が、バックエンドでのチップレット統合を支える基盤となります。高性能なチップレットを量産するためには、高性能な単一チップを効率的に製造できることが不可欠です。

今後の技術発展と先進パッケージングへの影響

記事はまた、ASMLが現在Intelによって導入されている「High-NA」(高開口数)EUVツールの開発を進めていることにも言及しています。これらのツールは、今後10年間のチップレットの超微細な特徴を定義するために必要です。パッケージングリソグラフィは通常、より古い技術(i-lineやステッパーなど)を使用しますが、コアチップレット自体は、先進パッケージングがサポートするように設計されている性能軌道を維持するために、EUVにおけるこれらの継続的なブレークスルーを必要とします。このEUV技術の進化は、半導体業界全体のロードマップを加速させ、次世代のAI、HPC、その他多くのアプリケーションの実現を可能にするでしょう。

コメント