背景

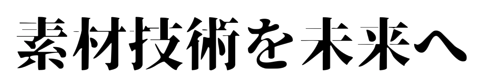

AI技術の急速な進化と普及は、データセンターにおける計算リソースの需要を劇的に押し上げています。しかし、高性能AI半導体は、その高い処理能力と引き換えに「発熱」「消費電力」「実装密度」という物理的な制約に直面しています。特に、データセンターの電力消費と冷却能力には限界があり、この問題を解決しなければ、AIのさらなる発展は滞ってしまいます。この課題に対処するため、半導体業界では、複数の小さなチップ(チップレット)を統合する「チップレット技術」や、チップを垂直に積み重ねる「3D積層技術」が次世代のソリューションとして注目されています。これらの技術は、チップ間の距離を短縮し、データ転送速度を向上させつつ、省電力化と高密度化を実現します。

主要内容

日本企業は、チップレットや3D積層といった先端パッケージング技術を支える精密技術において、世界的に極めて重要な役割を果たしています。具体的には、以下の企業がその卓越した技術でAI半導体の進化に貢献しています。

- TOWA: 3D積層されたHBM(高帯域幅メモリ)などのチップにおいて、微細な隙間に樹脂を真空状態で加熱しながら、優しくかつ完璧に充填する「コンプレッションモールド技術」を開発。この技術は、HBM製造における世界標準のシェアを独占しており、積層されたチップの信頼性と放熱性を確保する上で不可欠です。

- アオイ電子: チップレットを搭載するための高性能な基板製造において、革新的な技術を提供しています。高精度な配線形成と材料技術により、複数のチップレット間の高速な電気的接続と信号整合性を実現し、複雑なパッケージング構造を可能にしています。

- タツモ: 半導体ウェハやチップの精密な貼り合わせ技術で貢献しています。特に3D積層構造においては、異なる種類のチップを高い精度で位置合わせし、安定して接合する技術が不可欠であり、タツモの技術がその基盤を支えています。

- サムコ: 半導体チップの微細構造を彫刻するエッチング技術において、高い専門性を持っています。チップレット間の接続や、3D積層におけるスルーシリコンビア(TSV)などの形成において、非常に高い加工精度と制御性が求められるプロセスで重要な役割を担っています。

- テセック: AIサーバー向けチップが直面する過酷な熱環境を再現しながら、高速かつ正確な検査を行うテストハンドラー技術を提供しています。先端パッケージングされた高性能チップの品質保証には、極限状態での信頼性評価が不可欠であり、テセックの技術がそのテストプロセスを支えています。

影響・展望

これらの日本企業の精密技術は、AI半導体の発熱・電力・密度問題の解決に不可欠であり、チップレットや3D積層技術の実用化を強力に推進しています。日本の技術が世界の半導体サプライチェーンにおいて、特に後工程分野で確固たる地位を築いていることを示しており、次世代AIチップの開発競争における日本の優位性を裏付けています。今後、AIのさらなる高性能化と多様な応用が進むにつれて、これらの精密技術の需要は一層拡大すると予想されます。日本の企業は、引き続き技術革新をリードし、グローバルな半導体産業の発展に貢献していくでしょう。特に、PLP(パネルレベルパッケージング)のような次世代のパッケージング技術においても、日本の精密材料・装置技術が重要な役割を果たすことが期待されます。

コメント