背景:HBMテストの複雑化と自社開発の必要性

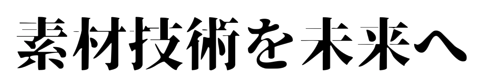

メモリアーキテクチャがチップレットのような統合へと移行するにつれて、メモリ製造とロジックパッケージングの境界線は曖昧になりつつあります。SK Hynixは、次世代HBM4(High Bandwidth Memory、第4世代)製品向けのシステムレベルテスト(SLT)装置の開発を完了したと報じられています。これまで、メモリがロジックプロセッサとどのように相互作用するかを確認するこのような検証は、主にTSMCのようなファウンドリやOSATsの領域でした。しかし、HBM4のような高度なメモリは、その統合の複雑さから、より精密で専門的なテストが必要とされています。

HBM4のアーキテクチャ変化とSLTの重要性

この装置の開発は、SK Hynixが「System-in-Package」(SiP)レベルの検査を社内で実施することを可能にします。これはHBM4にとって極めて重要です。なぜなら、これまでの世代とは異なり、HBM4のベースダイは、単純なメモリバッファではなく、ロジックウェハ(ファウンドリで製造される)である可能性が高いからです。このアーキテクチャの変更により、メモリスタックは特定のGPUまたはASICに供給されるカスタムチップレットとなり、その文脈で検証される必要があります。自社でこのテスト能力を持つことは、HBM4の性能と信頼性を確保し、顧客の要求に合わせたカスタマイズを可能にする上で決定的な意味を持ちます。

影響と今後の展望

このテスト能力を内製化することで、SK Hynixは歩留まりを向上させ、欠陥検出のフィードバックループを加速することを目指しています。この装置は、HBMがGPUと統合された実際の動作環境をシミュレートし、費用のかかる最終的なボンディングプロセスの前に互換性を確保します。これはHBMサプライチェーンにおける重要なプロセス革新であり、SK Hynixが「カスタムHBM」時代をより良くサポートできるよう位置づけています。AIや高性能コンピューティングの分野では、HBMの性能と信頼性がシステムの全体的な性能を大きく左右するため、このSLT技術は、次世代AIチップの進化を支える上で不可欠な要素となるでしょう。

コメント