背景と経済的推進要因

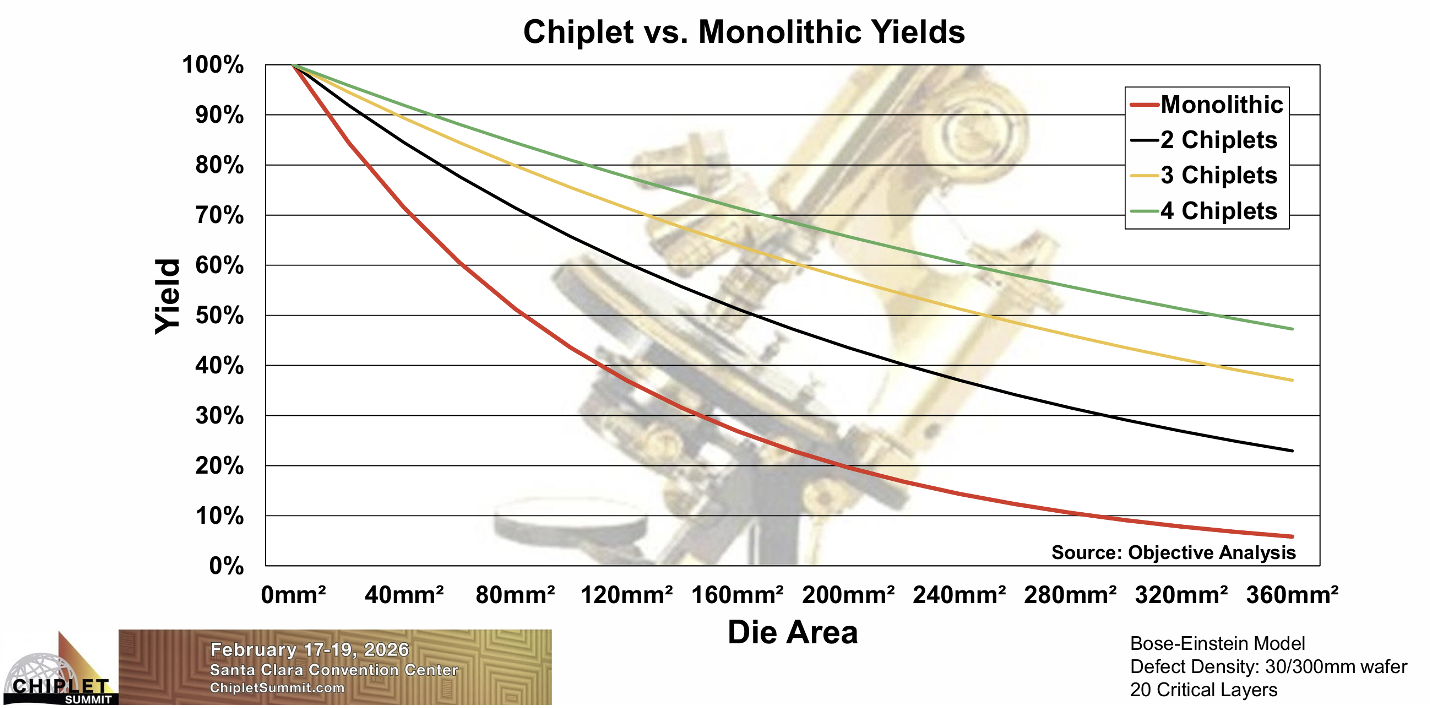

最近のチップレットサミットからの重要なポイントとして、チップレットが単なる斬新な設計コンセプトから、最先端のAIプロセッサにとって経済的に不可欠なものへと進化していることが強調されています。Objective Analysisのジム・ハンディ氏をはじめとする専門家は、先端ノード(例:3nm、2nm)における大規模なモノリシックダイは、指数関数的に低い歩留まりと、1セットあたり3000万ドルから5000万ドルにも及ぶ法外なマスクコストに悩まされていると指摘しています。チップレットは、これらの大規模な設計をより小さく、より高歩留まりのコンポーネントに分割することを可能にし、多くの場合、異なるプロセスノード(例:ロジックは2nm、I/Oは古いノード)を組み合わせてコストと性能を最適化します。これにより、従来の製造上の課題を克服し、イノベーションを継続するための新たな道が開かれています。

主要な技術と市場の展望

議論のかなりの部分は、チップレットを一体のユニットとして機能させるために必要な物理的相互接続に焦点が当てられています。本レポートは、次世代AIシステムに必要な高密度垂直スタッキングを実現するために、ハイブリッドボンディングが大幅に採用される(「非常に大きなものになる」)極めて重要な技術であると特定しています。チップレットはパッケージングに複雑さをもたらしますが、リソグラフィツールで印刷できる単一チップの物理的サイズ上限である「レチクル限界」を克服するために不可欠であると記事は指摘しています。この技術は、AIチップの性能向上と小型化において中心的な役割を果たすでしょう。また、2025年の半導体業界全体の収益に匹敵する6000億ドル規模に達すると予測されており、この成長は、ハイパースケーラーとAI企業の設備投資によってほぼ独占的に牽引されています。これらの企業のAIインフラへの支出は近年倍増しています。

影響と今後の展望

チップレットは、従来のムーアの法則のスケーリングが鈍化しているにもかかわらず、このスケーリングを継続させる主要なイネーブリング技術であると結論付けられています。特に、高性能コンピューティング(HPC)やAIといった分野では、チップレットによる性能向上とコスト削減が不可欠です。複数のチップを統合することで、個々のチップの製造歩留まりを向上させつつ、より複雑で強力なシステムを構築することが可能になります。これにより、AIの進化を支えるハードウェア基盤が強化され、データセンターやエッジデバイスにおけるAIアプリケーションの普及がさらに加速すると見込まれます。この技術の進展は、半導体産業全体の構造を根本から変革し、新たな技術革新の波を生み出すでしょう。

元記事: https://semiengineering.com/chiplets-2026-where-are-we-today/

コメント