【概要】 世界最大の半導体製造メーカーであるTSMCが、AIチップなどの高性能な半導体を組み立てる新しい方法「CoPoS(コポス)」の導入を進めています。これまでの丸い板(ウェハー)を使う方法から、巨大な四角いパネルを使う方法に切り替えることで、一度により多くのチップを効率よく、安く作ることが可能になります。2026年にも試験ラインを稼働させ、2028年後半以降の本格的な量産を目指しています。

【詳細】 現在、AIに使われる高性能なチップ(NVIDIAのBlackwellなど)の多くは、TSMCの「CoWoS(コワース)」という技術を使って組み立てられています。しかし、AIの進化に伴い、チップのサイズがどんどん大きくなっており、従来の丸いシリコンウェハーでは効率が悪くなってきました。そこでTSMCが開発しているのが、四角いパネルを利用した新しい技術「CoPoS」です。

従来の「丸い板」から「四角いパネル」への転換

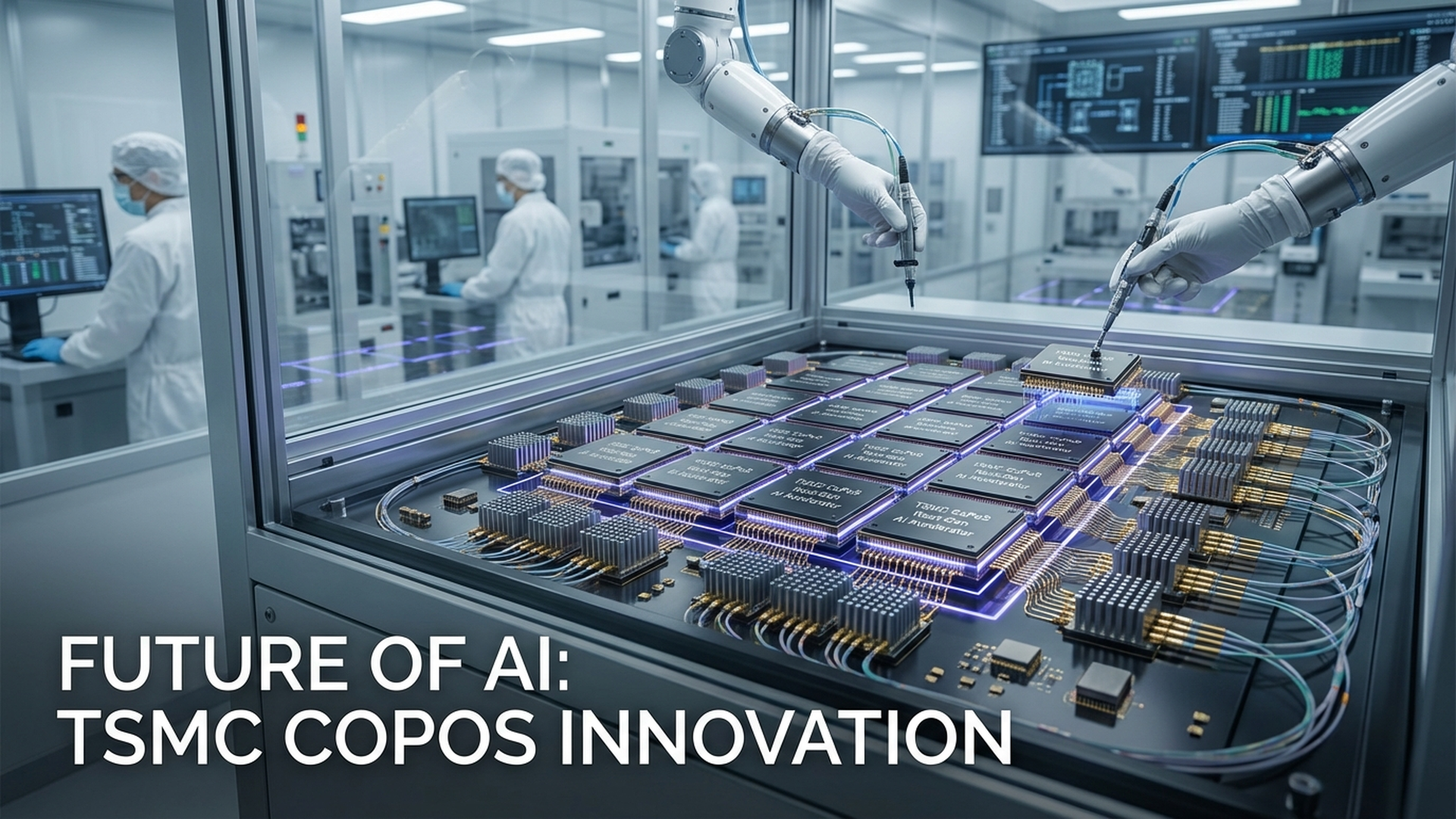

これまでの製造プロセスでは、直径300mmの丸いシリコンウェハーが使われてきました。しかし、四角いチップを丸い板の上に並べると、どうしても端の部分にムダなスペースができてしまいます。

- 面積の拡大: 新しい技術では、最終的に750×620mmという非常に大きな四角いパネルを使用します。

- 効率アップ: 四角いパネルを使うことで、端のムダを減らし、一度に作れるチップの数を大幅に増やすことができます。

- 巨大チップへの対応: 将来のAIアクセラレータは、より多くのメモリ(HBM)や演算ユニットを1つのパッケージに詰め込む必要がありますが、パネル方式ならそのスペースを確保しやすくなります。

導入のスケジュールと技術的背景

この「CoPoS(Chip-on-Panel-on-Substrate)」は、従来のCoWoSの考え方と、パネルレベルのパッケージング技術を組み合わせたものです。

- 素材の変化: シリコンの代わりに、ガラスやサファイアといった素材のパネルの上に配線層を作ることが検討されています。

- 量産時期: 2026年に試験的なラインを立ち上げ、2028年末から2029年前半にかけて本格的な量産が始まる見通しです。

- 製造拠点: 台湾の嘉義(チャイイー)にある新しい工場「AP7」で主に生産される予定で、将来はアメリカのアリゾナ州にある工場でも対応が計画されています。

この技術革新により、今後さらに巨大化・複雑化するAI用チップを、より低コストで安定して供給できるようになると期待されています。

元記事: TSMC Prepares CoWoS to CoPoS Shift with 750 × 620 mm Panels – TechPowerUp 収集日: 2024年5月22日(※記事公開日に基づく情報を参照)

コメント